# DLC9500P24 控制板功能说明

版本: REV-1.3

作者: 王忠宝 2014/11/4

- 1、增加 ADC 处连接器的说明

- 2、增加尺寸说明

- 3、将 DLC4100V6P24 修改成 DLC500P24

## **Overview**

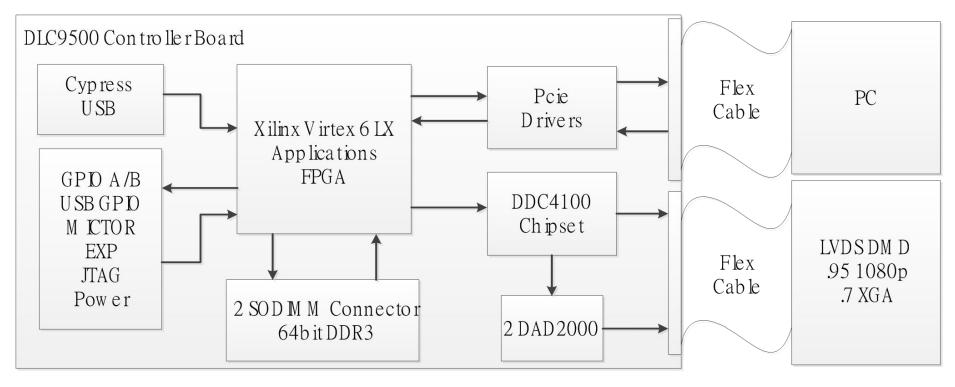

DLC9500P24 投影设备是采用了当今先进的数据处理技术以及高速接口进行设计的投影系统,其核心的数据收发、处理与控制单元采用了 Xilinx 公司资源非常丰富的 Virtex-6 系列芯片,即 XC6VLX240T-1FFG1156 FPGA 可编程逻辑器件。DLC9500P24 投影设备比以前同类 DLP4100 产品的性能指标有几何级别的提高和改善。下图为 DLC9500P24 的功能图。

Figure-1 DLC9500P24 Block Diagram

# **Key Components**

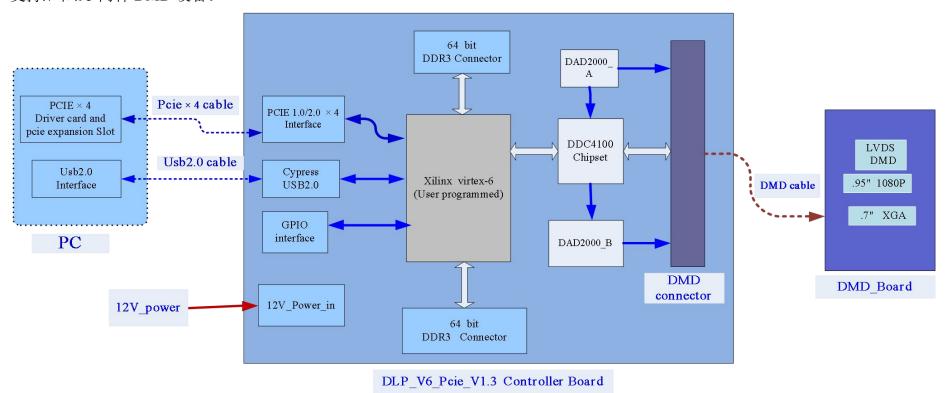

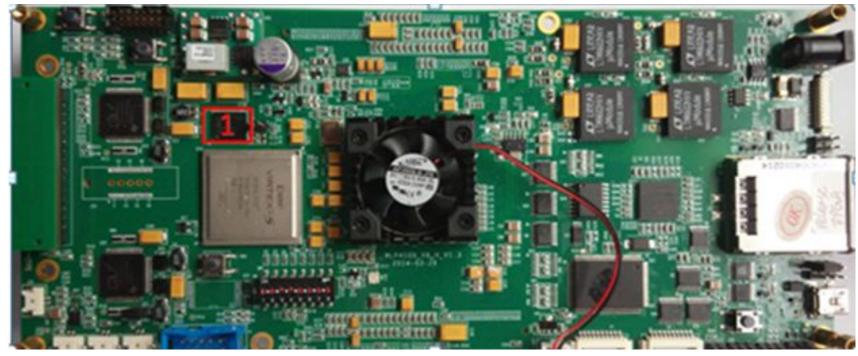

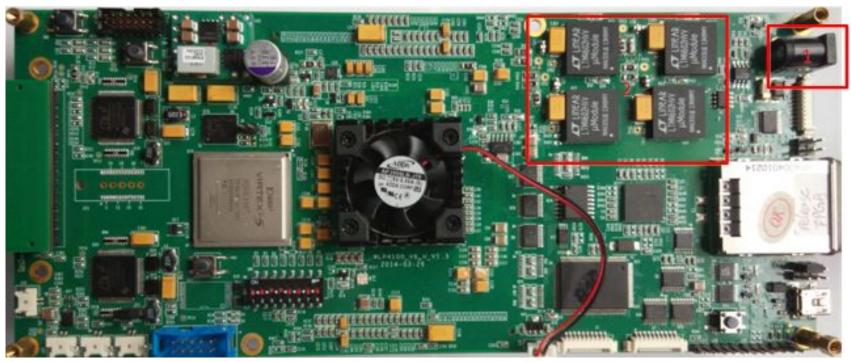

下图包含了 DLC9500P24 设备的最主要组成元件。从下图可以看出, DLC9500P24 设备可以工作于 PCIe 模式或者 USB 模式下, 且支持.7 和.95 两种 DMD 设备。

Figure-2 Key Components

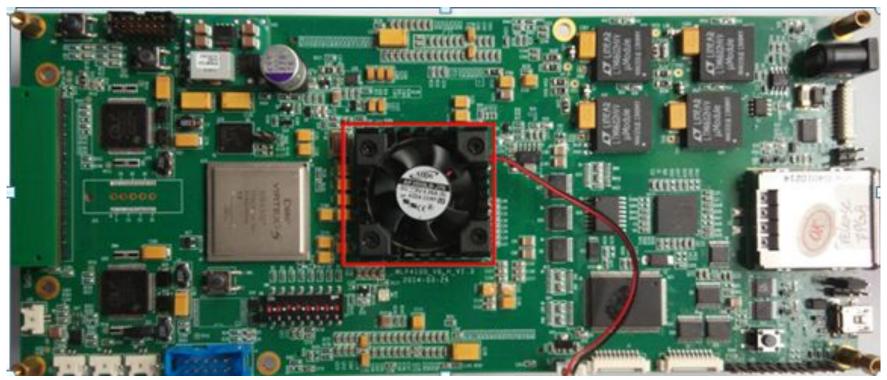

#### Xilinx Virtex 6 APPSFPGA

上图红色线框的风扇下面是 Virtex-6 FPGA XC6VLX240T-1FFG1156 芯片。该芯片用于实现 PCIe 接口、DDR3 接口、USB 接口、通用的 GPIO 接口以及实现对 DDC4100(即 Virtex-5)芯片的控制与操作。该芯片是整个 DLC9500P24 控制板的功能控制与数据处理单元,相当于设备的 CPU 芯片。该芯片支持 PCIe 与 DDR3 接口,并且逻辑资源与时钟资源丰富,极大地提高了设备的性能。

#### **DDC4100 Controller**

上图红色线框的 Virtex-5 芯片是 DDC4100 模块,由 TI 公司提供其内部工作程序,最终实现对 DMD 镜元模块的控制。 (1) 为 DMD 提供 32bit/64bit 400MHz DDR LVDS 高速数据接口; (2) 为 DMD 提供控制接口,实现对 DMD 初始化流程以及复位的控制; (3) 对 DAD2000 上电与复位芯片进行控制;

#### **DAD2000 Reset Drivers**

上图红色线框的芯片是两片 DAD2000 芯片,实现对 DMD 镜元上电和复位的功能: (1)实现对 DMD 镜面 16 个块复位控制; (2)单片 DAD2000 工作在 XGA (.7 DMD) 模式,两片 DAD2000 工作在 1080P (.95 DMD) 模式 (3)为 DMD 提供较高电压的供电电源;

## **50MHz Oscillator**

上图红色线框部分为 50MHz 的系统晶振,为 Virtex-6 FPGA,即数据处理与控制芯片提供工作所必须的时钟。

#### **USB Controller**

上图红色线框 1 所示为 USB2.0 芯片 (PCB 位置: U21)。该芯片实现 USB 接口功能,将最终的控制与数据信息发送给 FPGA 芯片。红色线框 2 为 USB2.0 (PCB 位置: J12) 插口。用户在实际开发与使用中,可以通过 USB 接口实现对 DLC9500P24 设备的控制,包括发送控制命令、图片数据以及调试命令。红色线框 3 所示芯片是 EPROM (PCB 位置: U22),为 USB 芯片提供工作所需的程序。

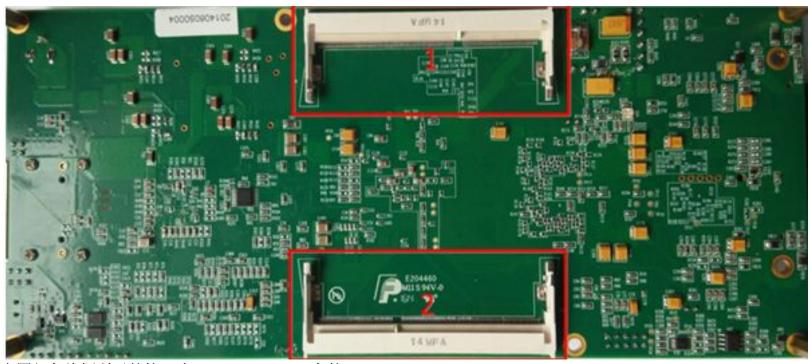

## **DDR3 SODIMM Connector**

上图红色线框所示的接口为 DDR3 SODIMM 条接口:

| 容量  | SODIMM 端口宽度 | DDR3 速率          | 物理 RANK |

|-----|-------------|------------------|---------|

| 2GB | 64bit       | 800Mbps          | 单 RANK  |

| 4GB | 64bit       | 可使用 2GB @800Mbps | 双 RANK  |

| 8GB | 64bit       | 可使用 4GB @800Mbps | 双 RANK  |

### PCIe interface

上图红色线框 1 所示为 PCIe 设备连接器(PCB 位置: J4),实现与 PC 机的互联。红色线框 2 所示为 PCIe 驱动器,增加 PCIe 设备驱动能力。PCIe 接口用于连接电脑 PC 机,实现用户对 DLC9500P24 板的控制,包括传输图片数据、控制命令、调试命令等,功能与USB 接口一致。

## **Configuration PROMs**

上图红色线框的芯片是 DDC4100(Virtex-5 FPGA)加载程序的 PROM 芯片,该芯片用于固化 TI 公司提供的 Virtex-5 芯片的程序。

## Connectors

| 红色线框 | 端口功能描述                                                                  |  |  |

|------|-------------------------------------------------------------------------|--|--|

| 0    | DMD 连接器:用于连接 DMD 镜元设备。 DLC9500P24 设备支持.7 和.95 两种规格的 DMD 设备,但是仅需要一种连接线缆; |  |  |

| 1    | USB GPIO 接口连接器:用于 USB 接口的 GPIF 模式,专供 TI 使用;                             |  |  |

| 2    | GPIO A 接口连接器 (9-PIN): 通用接口,具体功能可以根据用户需求进行修改;                            |  |  |

| 3    | GPIO B接口连接器 (9-PIN): 通用接口,具体功能可以根据用户需求进行修改; GPIOA/B 一共 18 个 PIN。        |  |  |

| 4    | PCB 位置 J19: 该接口连接到内部的 ADC 芯片,提供一路模拟信号输入,供用户使用;                          |  |  |

| 5    | PCB 位置 J20: 该接口连接到内部的 ADC 芯片,提供一路模拟信号输入,供用户使用;                          |  |  |

| 6    | PCB 位置 J18: 该接口连接到内部的 ADC 芯片,提供一路模拟信号输入,供用户使用;                          |  |  |

| 7    | PCB 位置 J17: 该接口连接到内部的 ADC 芯片,提供一路模拟信号输入,供用户使用;                          |  |  |

| 8    | PCB 位置 J21: 将 J17~J20 的模拟输入转换成数字信号输出给用户;同时也可以将 PWM 信号输出给用户。             |  |  |

| 9    | JTAG 连接器: 1、实现 FPGA 在线调试功能(主要用于开发);<br>2、实现 FPGA 程序固化功能;                |  |  |

| 10   | 图中 8 附近的拨码开关现在不可用,我查了 pdf 文档以及 FPGA 设计; FPGA 目前并未使用该开关。                 |  |  |

| 背面   | U42: 该芯片为 PWM 输出芯片,可以由 4~7 连接器的模拟输入(即 J19~J20)驱动。                       |  |  |

# **Power Supplies**

红色线框 1 所示为 12V/5A 电源输入接口 (PCB 位置: J3)。红色线框 2 为电源管理芯片。

# 按键

| 按键 | 按键 1 | 按键 2                        | 按键3  | 按键 4             |

|----|------|-----------------------------|------|------------------|

| 功能 | 全局复位 | 复位 Virtex-6 FPGA 的 DMD 驱动程序 | 电源复位 | Virtex-6 FPGA 复位 |

# 状态指示灯

| LED |                       | 功能描述                                   |  |

|-----|-----------------------|----------------------------------------|--|

|     |                       | USB 模式/PCIe 模式                         |  |

| 1   | D26(USB下载数据指示灯)       | D26 上电灭, USB 下载数据时常亮;                  |  |

| 2   | D3(工作指示灯)             | D3 上电熄灭;                               |  |

| 3   | D2(工作指示灯)             | D2 上电常亮;                               |  |

| 4   | D1(工作指示灯)             | D1 上电闪烁;                               |  |

| 5   | D4(USB或 PCIe 下载数据指示灯) | D4 上电灭,USB 或 PCIe 下载数据是常亮;             |  |

| 6   | D17(DDC 配置指示灯)        | D17 正常工作状态: 刚上电时由红色闪烁为绿色,说明此时 DDC4100  |  |

|     |                       | 正在配置,最后变为红色表示配置成功;                     |  |

| 7   | D20(背部) (FPGA 配置指示灯)  | D20 正常工作状态: 刚上电时由红色闪烁为绿色,说明此时 APPSFPGA |  |

|     |                       | 正在配置,最后变为红色表示配置成功                      |  |

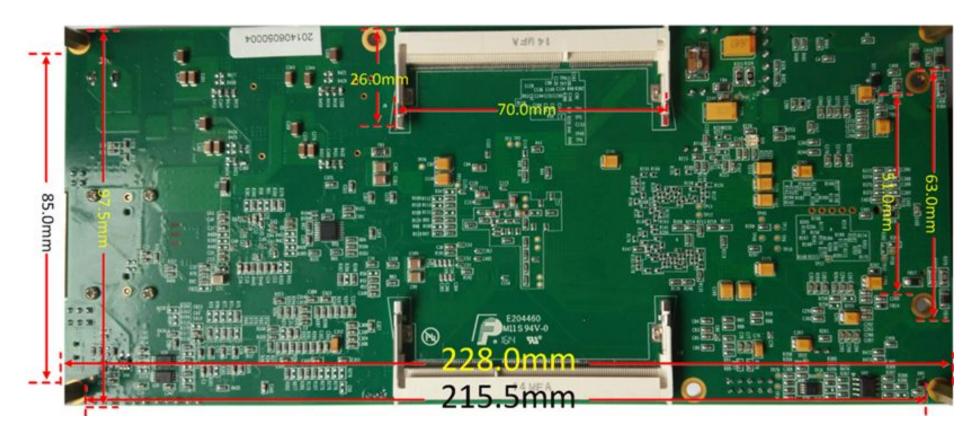

# 尺寸:

注意:图中尺寸的有效值为毫米(mm),小数点后数据为估计值。

注意: DLC9500P24 设备支持.7 和.95 两种规格的 DMD 设备,尺寸文件为 dmd\_dev\_spec.dxf